|

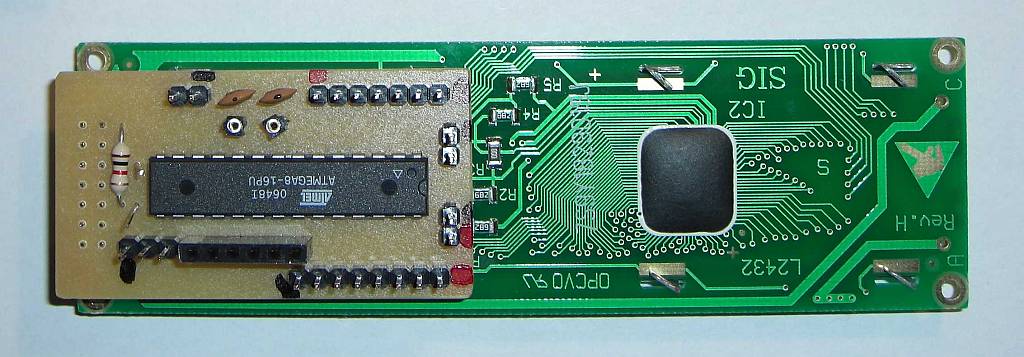

Zum Funktionsgenerator folgende Grundüberlegungen: Ein Byte (Zahlenwert von 0-255) wird an einen Port gegeben.An diesem hängt

ein R2R-Widerstandsnetzwerk der den binär am Port anliegenden Zustand in eine Spannung umsetzt, somit sind 256 Spannungswerte darstellbar.

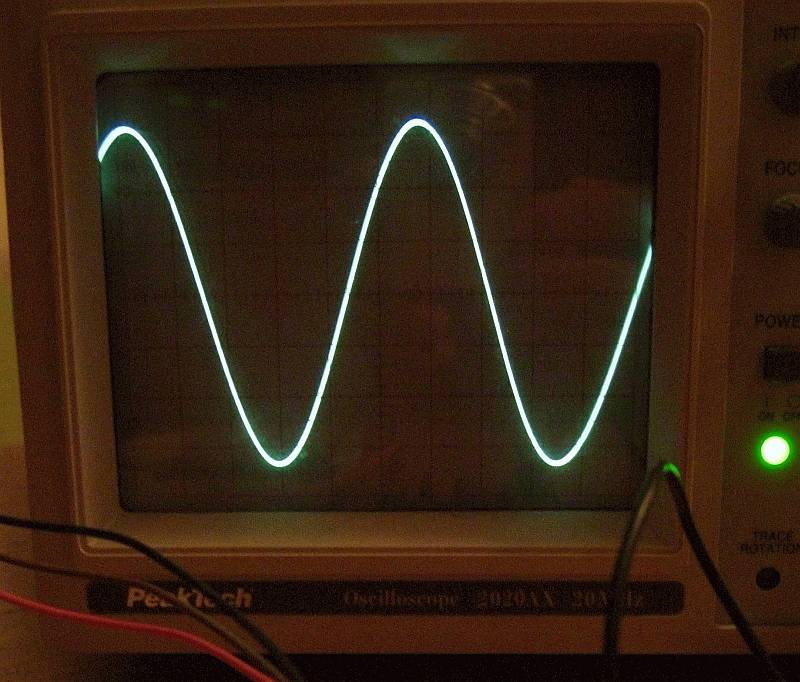

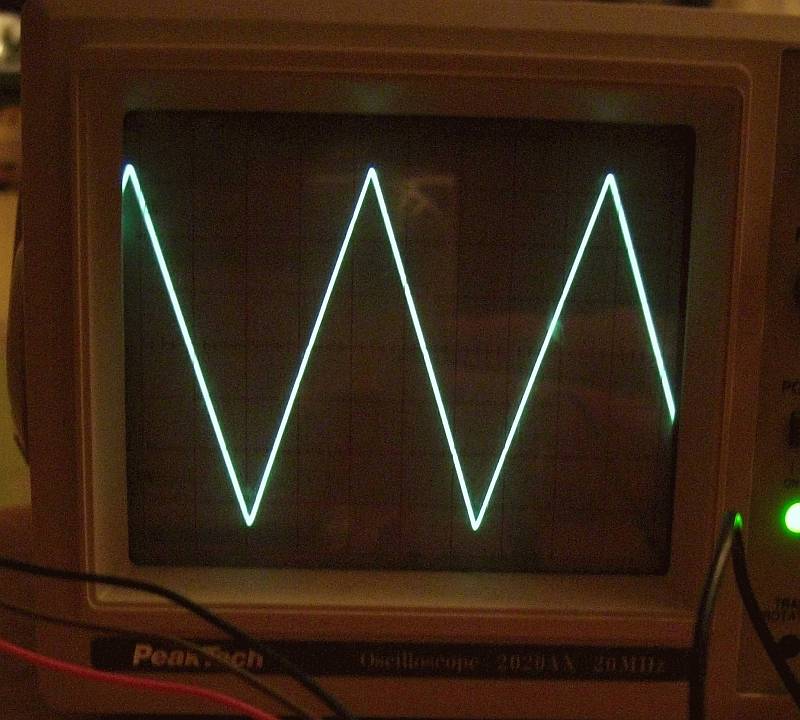

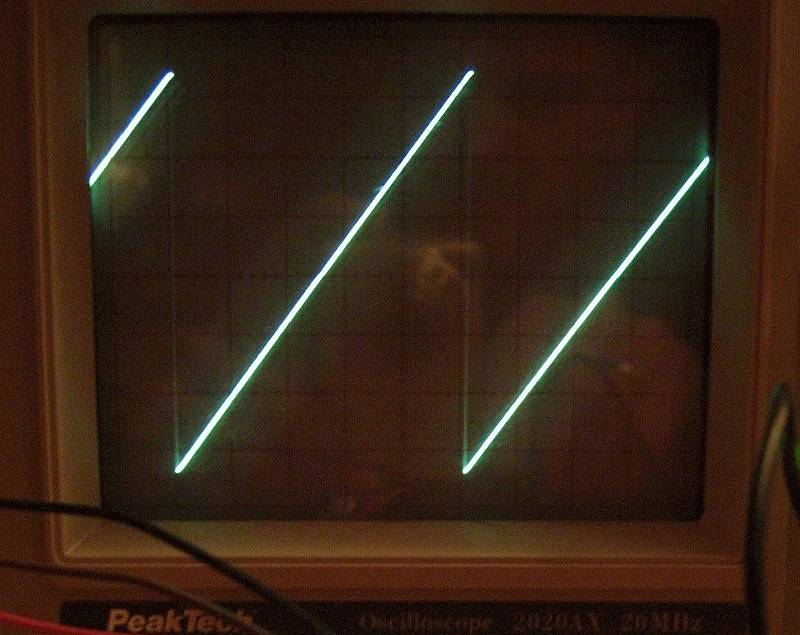

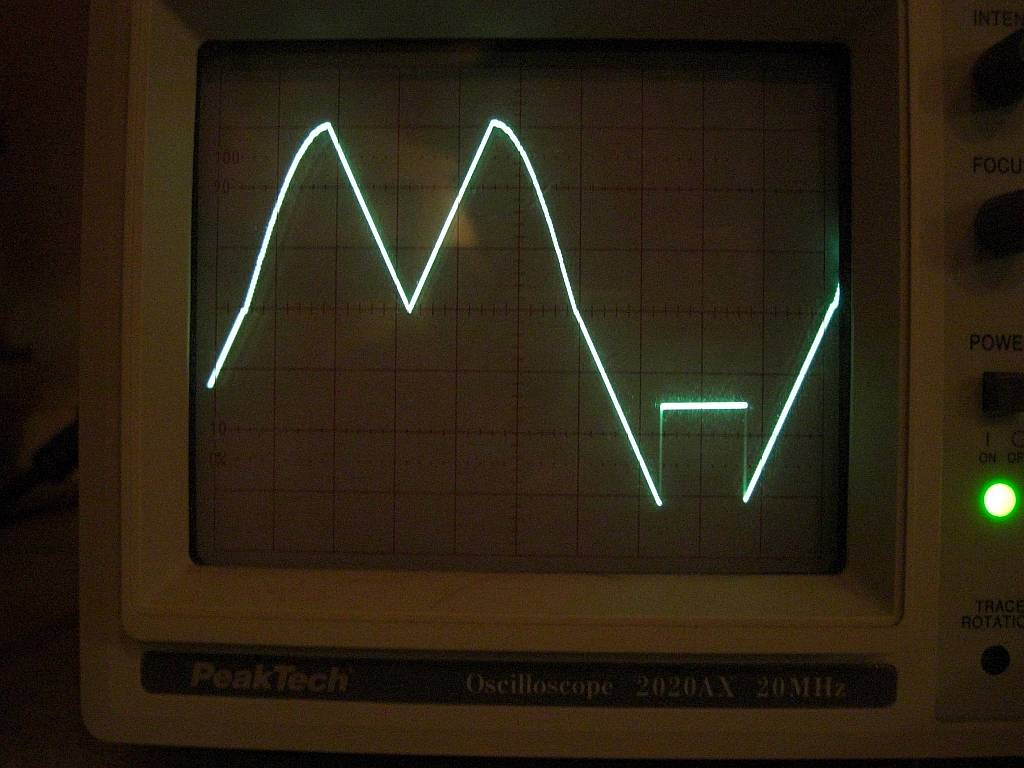

Geplant waren folgende Funktionen Sinus, Dreieck, Sägezahn, Rechteck. In wie viele Teilschritte zerlegt man nun solche Funktionen am sinnvollsten? Bei einem

Sägezahn wären 256 Teilschritte am sinnvollsten, bei einer Dreieckfunktion 512, bei einem Rechteck 2 und bei einem Sinus? Schön wäre es ja

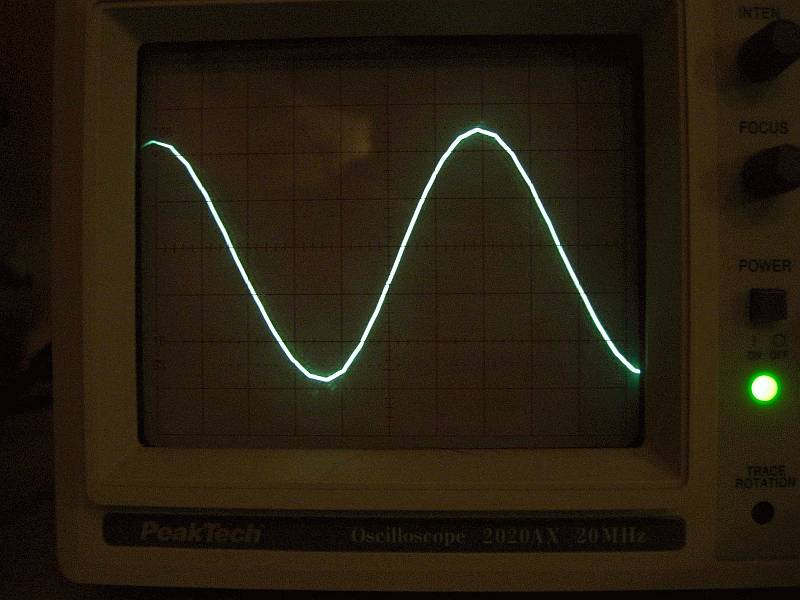

einen Sinus in 360 Schritte zu zerlegen, so hätte man je 1 Grad einen Spannungswert. Allerdings ist die Zerlegung eines Kreises in 360° eine menschengemachte Konvention. Genausogut hätte man ihn auch in 200, 256, 400 oder 512 Teile zerlegen können. Die historischen Hintergründe für 360° sind mir nicht bekannt. Wie dem auch sei, ich entschied mich alle Funktionen einheitlich mit 256 Teilschritten aufzulösen. Damit habe ich bei einer Sägezahnfunktion einheitliche Schritte von 5V / 256Schritte = 0.02V. Bei der Sinusfunktion sieht das schon anders aus. Da habe ich in den flachen Bereichen der Kurve einige Schritte, an denen die Ausgangsspannung sich nicht ändert und in den steilen Flanken Sprünge von 3 Schritten, also 0.06V. Das allerdings bei einer Amplitude von 5V Vss. Reduziert man die Amplitude auf 1V Vss, wie man sie im Audioverstärkerbereich benötigt, so sind das allerdings nur noch Sprünge von 0.012V.

Die Auflösung in 256 Teilschritte führt zu folgender Problematik: Um einen Zahlenwert an einen Port eines Atmegas zu geben, benötigt man 2 Systemtakte.

Ist die Funktion in 256 Teilschritte aufgelöst, benötigt man somit 512 Systemtakte für

einen kompletten Durchlauf der Funktion. Atmegas werden normalerweise mit max. 16MHz getaktet. Dadurch ergibt sich eine maximal mögliche Augangsfrequenz des Funktionsgenerators von 16.000.000 : 512 = 31250Hz. Nun möchte man aber keine fest eingestellte Frequenz haben, sondern diese einstellen können. Soll der Atmega sich nun "nebenbei" noch um irgendwelche Timings kümmern und man das programmtechnisch (weiß der Henker wie) irgendwie hinbekommt das jeder 10. Systemtakt zu einer Ausgabe führt, läge die Maximalfrequenz nur noch bei 6250Hz. Diese Frequenz lässt sich dann nur noch dadurch steigern, dass man wie bei der DDS-Synthese üblich Teilschritte der Funktion weglässt, also quasi mit einer geringeren Auflösung fährt. Um so wieder auf 31250Hz zu kommen, müsste man 4 von 5 Teilschritten der Funktion auslassen. Somit würde die Funktion nur noch aus 51 Werten bestehen. Und wenn die Frequenz noch höher werden soll???

Natürlich kann ich mittels passender Filter am Ausgang aus einem Sinus bestehend aus 20 Teilschritten noch so was "hinbiegen" was einem Sinus

ähnlich sieht, aber dann kann ich auch gleich meinen alten analogen Funktionsgenerator weiternutzen...

Ich entschied mich deshalb dazu den Takt für den Prozessor von aussen mittels eines Rechteckgenerators zuzuführen und dessen Frequenz einstellbar zu

gestalten. Somit hätte ich dann tatsächlich die gewünschten 31250Hz am Ausgang. Ein Test auf meinem Steckbrett verlief wie gewünscht und es stellte sich heraus, das der Atmega8 ohne mit der Wimper zu zucken

Taktgeschwindigkeiten von fast 40MHz schluckt!!! Warum sollte er auch nicht, immerhin ist er ein CMOS und die können so was heutzutage. Bei diesen Frequenzen wird er nicht mal das geringste bisschen warm, lediglich

die Stromaufnahme steigt deutlich an. Na und? sollte ja kein Energiespargerät werden. ;-)

Bei der Umsetzung in die Praxis habe ich mich dann jedoch mit knapp 30MHz Taktfrequenz begnügt, so dass ich am Ausgang

noch gute 50000Hz zu Verfügung habe.

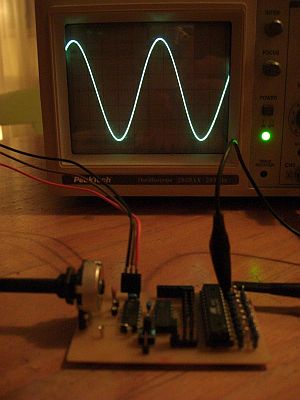

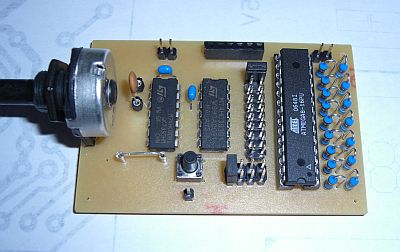

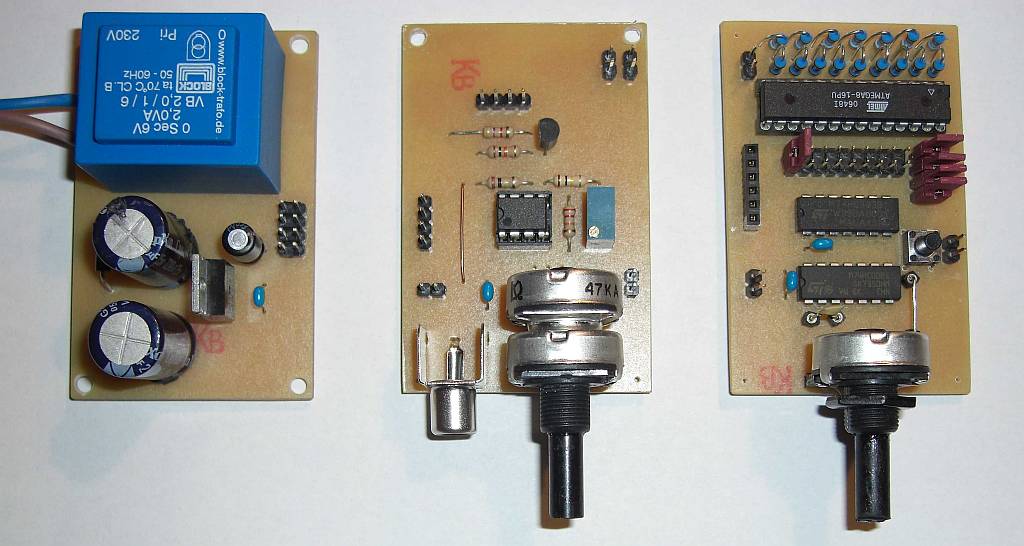

Herrausgekommen ist dann letztlich folgende Schaltung:

|